This article was downloaded by: [University Of Gujrat]

On: 11 December 2014, At: 13:44

Publisher: Taylor & Francis

Informa Ltd Registered in England and Wales Registered Number: 1072954 Registered

office: Mortimer House, 37-41 Mortimer Street, London W1T 3JH, UK

### Molecular Crystals and Liquid Crystals

Publication details, including instructions for authors and subscription information:

http://www.tandfonline.com/loi/gmcl20

# Effects of Polystyrene Gate Dielectrics with Various Molecular Weights on Electrical Characteristics of Pentacene Thin-Film Transistors

Sung Woo Lee<sup>a</sup>, Dong Wook Kim<sup>a</sup>, Hyunji Shin<sup>a</sup>, Jong Sun Choi<sup>a</sup>, Jin-Hyuk Bae<sup>b</sup>, Xue Zhang<sup>c</sup> & Jaehoon Park<sup>c</sup>

- <sup>a</sup> Department of Electrical, Information and Control Engineering, Hongik University, Seoul, Republic of Korea

- <sup>b</sup> School of Electronics Engineering, Kyungpook National University, Daegu, Republic of Korea

- <sup>c</sup> Department of Electronic Engineering, Hallym University, Chuncheon, Republic of Korea

Published online: 17 Nov 2014.

To cite this article: Sung Woo Lee, Dong Wook Kim, Hyunji Shin, Jong Sun Choi, Jin-Hyuk Bae, Xue Zhang & Jaehoon Park (2014) Effects of Polystyrene Gate Dielectrics with Various Molecular Weights on Electrical Characteristics of Pentacene Thin-Film Transistors, Molecular Crystals and Liquid Crystals, 598:1, 129-134, DOI: <a href="https://doi.org/10.1080/15421406.2014.933384">10.1080/15421406.2014.933384</a>

To link to this article: <a href="http://dx.doi.org/10.1080/15421406.2014.933384">http://dx.doi.org/10.1080/15421406.2014.933384</a>

#### PLEASE SCROLL DOWN FOR ARTICLE

Taylor & Francis makes every effort to ensure the accuracy of all the information (the "Content") contained in the publications on our platform. However, Taylor & Francis, our agents, and our licensors make no representations or warranties whatsoever as to the accuracy, completeness, or suitability for any purpose of the Content. Any opinions and views expressed in this publication are the opinions and views of the authors, and are not the views of or endorsed by Taylor & Francis. The accuracy of the Content should not be relied upon and should be independently verified with primary sources of information. Taylor and Francis shall not be liable for any losses, actions, claims, proceedings, demands, costs, expenses, damages, and other liabilities whatsoever or howsoever caused arising directly or indirectly in connection with, in relation to or arising out of the use of the Content.

This article may be used for research, teaching, and private study purposes. Any substantial or systematic reproduction, redistribution, reselling, loan, sub-licensing, systematic supply, or distribution in any form to anyone is expressly forbidden. Terms &

Conditions of access and use can be found at <a href="http://www.tandfonline.com/page/terms-and-conditions">http://www.tandfonline.com/page/terms-and-conditions</a>

Mol. Cryst. Liq. Cryst., Vol. 598: pp. 129–134, 2014 Copyright © Taylor & Francis Group, LLC

ISSN: 1542-1406 print/1563-5287 online DOI: 10.1080/15421406.2014.933384

## Effects of Polystyrene Gate Dielectrics with Various Molecular Weights on Electrical Characteristics of Pentacene Thin-Film Transistors

SUNG WOO LEE,<sup>1,†</sup> DONG WOOK KIM,<sup>1,†</sup> HYUNJI SHIN,<sup>1</sup> JONG SUN CHOI,<sup>1,\*</sup> JIN-HYUK BAE,<sup>2</sup> XUE ZHANG,<sup>3</sup> AND JAEHOON PARK<sup>3,\*</sup>

<sup>1</sup>Department of Electrical, Information and Control Engineering, Hongik University, Seoul, Republic of Korea

<sup>2</sup>School of Electronics Engineering, Kyungpook National University, Daegu, Republic of Korea

<sup>3</sup>Department of Electronic Engineering, Hallym University, Chuncheon, Republic of Korea

We report on the molecular weight effect of polystyrene (PS) gate dielectric on the characteristics of pentacene thin-film transistors. Dielectric layers were formed by using three different PS molecules of high molecular weight (PS-H) and low molecular weight (PS-L), and their blend (PS-B). The transistor having the PS-H gate dielectric exhibited the most pronounced drain currents as well as mobility. The gate-leakage current for the device with PS-H was even lower by one order of magnitude than that for the device with PS-L. The results are explained with the relationship between the surface characteristics of gate dielectric layer together with pentacene grain size and the transistor performances.

**Keywords** Organic transistor; gate dielectric; polystyrene; molecular weight

#### Introduction

Gate dielectric materials play a key role in improving the performance of organic thinfilm transistors (OTFTs) [1]. For example, the gate dielectric layer determines the grain growth and molecular orientation of organic semiconductor in OTFTs. Since the conducting channel in OTFTs is formed in close proximity to the interface between a gate dielectric layer and an organic semiconductor layer, the surface properties of gate dielectric layer in terms of morphological roughness and surface energy must be of primary importance for the device performance [2, 3]. In addition, the leakage current through a gate dielectric layer

<sup>&</sup>lt;sup>†</sup>These authors contributed equally to this work.

<sup>\*</sup>Address correspondence to Jong Sun Choi, 72-1 Sangsu-dong, Mapo-gu, P-420, Seoul 121-791, Korea. Tel.: +82-2-320-3097; Fax: +82-2-320-1193. E-mail: jschoi@wow.hoongik.ac.kr; and Jaehoon Park, 1 Hallymdaehakgil, Chuncheon, Gangwan-do 200-702, Korea. Tel.: +82-33-248-2357; Fax: +82-33-242-2524. E-mail: jaypark@hallym.ac.kr

Color versions of one or more of the figures in the article can be found online at www.tandfonline.com/gmcl.

is required to be as low as possible, which is one of significant factors for designing OTFT-based integrated circuits [4]. To date, polymer-based gate dielectric materials have been emerged as a natural component for OTFTs. This is owing to their unique advantages such as mechanical flexibility and low-temperature processability. Therefore, a number of works in this research area have focused on OTFTs with polymeric gate dielectrics. Nevertheless, there are few reports on the effects of molecular weights of polymer gate dielectrics on the characteristics of OTFTs, which are definitely informative for understanding device physics and further advancements of OTFTs.

In this study, we have prepared three different gate dielectric layers using different molecular weights of polystyrene (PS), i.e. Mw 288,000 for high molecular weight PS-H and 45,000 for low molecular weight PS-L and their blend (PS-B) for PS-H:PS-L = 1:1, respectively. Top-contact structured OTFTs are fabricated to investigate the underlying effects of the fabricated gate dielectric layers on the device performance. The surface morphology and surface energy of gate dielectrics are also analyzed with atomic force microscopy (AFM) and contact angle measurements.

#### **Experimental**

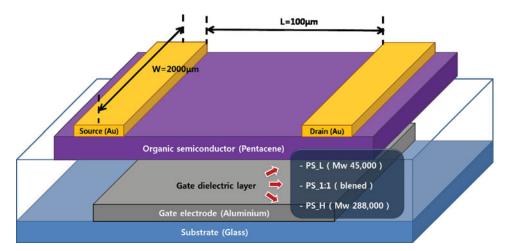

For the fabrication of OTFTs with top-contact source/drain structure, a glass (Marienfeld 17167) substrate was sequentially cleaned with acetone, iso-propyl alcohol and deionized water. Then, a 150-nm-thick aluminum gate electrode was thermally evaporated onto a glass substrate by using a first shadow mask. Next, different types of PS (Aldrich Co. Ltd), which are PS-H, PS-B, and PS-L, were dissolved into toluene solvent. In order to obtain comparable thickness of a gate dielectric layer, different weight percents for the PS solution (4.3 wt%, 5.4 wt%, 7.0 wt%) were used for PS-H, PS-B and PS-L, respectively. After filtering PS solutions using a 0.45- $\mu$ m syringe filter, PS dielectric layers were formed by spin-coating and baked for 3 hours at 140°C in dry vacuum oven. Thicknesses of the fabricated gate dielectric layers were almost same as  $320 \pm 15$  nm in each device. Pentacene (TCI Co. LTD) layer, as an organic semiconducting layer, was thermally evaporated through a second shadow mask onto the gate dielectrics with the deposition rate of 0.1 nm/s up to the thickness of 60 nm. Finally, 50-nm-thick gold source and drain electrodes were thermally evaporated using a third shadow mask. The fabricated device configuration is depicted in Fig. 1. During the fabrication processes, all of the vacuum depositions were performed under the base pressure of  $1.6 \times 10^{-6}$  Torr. The channel width and length for the fabricated device are 2000 and 100  $\mu$ m, respectively.

Electrical characterizations were performed with impedance analyzer (HP 4192LF, Agilent Technologies) and semiconductor analyzer (EL 421C, Elecs Co.). The surface characteristics of films were analyzed with AFM (XE-150, PSIA Inc.) and contact angle measurements.

#### **Results and Discussion**

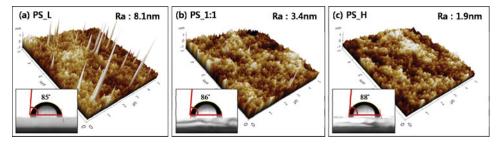

Figure 2 shows the AFM images of the three different gate dielectric layers. The surface morphology together with surface roughness was determined from each AFM data scanned in the area of 5  $\mu$ m  $\times$  5  $\mu$ m. As observed in Fig. 2, the PS-H film exhibits the smoothest surface among the three different types of the fabricated films. The average roughness values of the three gate dielectric layers are measured to be about 8.1, 3.4 and 1.9 nm for PS-L, PS-B (i.e. PS\_1:1) and PS-H, respectively. Since the PS molecules show relatively hydrophobic nature, it is deduced that higher molecular weight would lead rather smooth

Figure 1. A schematic diagram of a fabricated pentacene TFT with a polymeric insulator having different molecular weight.

surface within the thin-film formation. The fact that polymer chain-ends are closely related to the physical properties of a polymer also implies that the chain ends in the PS-H film might be densely packed, compared to the PS-L case [5]. Further analyses on the packing density of PS chain ends on the film surface are required to elucidate the morphological change arising from different MWs. In addition, this study analyzed the surface energies of the fabricated PS films, which was determined from the magnitude of contact angle. Previously, it was reported that the surface energy of PS films is essentially independent of MW when MW  $\geq$  8,000 [6,7]. Likewise, the magnitude of contact angle of deionized water drop on each surface exhibits almost same as  $86 \pm 2^{\circ}$  in our results, as shown in the insets of Fig. 2. Hence, the effect of surface energies would be ignorable.

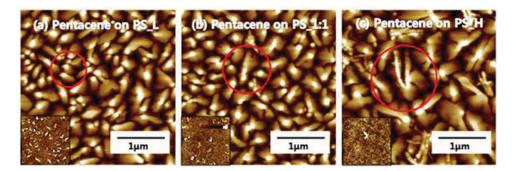

Figure 3 shows the corresponding AFM images of the 60-nm-thick pentacene layers grown on each gate dielectric layer. The grain size and feature of the pentacene films were determined from each AFM data scanned in the area of  $5 \mu m \times 5 \mu m$ . Note that the shape of grain for pentacene films is dendritic, which is in good agreement with previous works employing polymeric insulators for pentacene devices [8]. From Fig. 3, the grain sizes are measured to be about 0.3, 0.5 and 1.0  $\mu m$  in its diameter for those on PS-L, PS-B (i.e. PS\_1:1) and PS-H, respectively. Meanwhile, Choi et al. reported that the morphologies and

**Figure 2.** AFM and contact angle images of gate dielectric surface. (a) PS-L, (b) PS-B (i.e. PS\_1:1) and (c) PS-H gate dielectric films, respectively. Ra is the abbreviated term of average roughness of gate dielectric surface.

**Figure 3.** AFM images of 60-nm-thick pentacene layers grown on (a) PS-L, (b) PS-B (i.e. PS\_1:1), and (c) PS-H gate dielectric films. The circle indicates the average grain size in each pentacene film. Inset shows the corresponding initial growth of pentacene molecules at the interface.

crystalline ordering of the pentacene films deposited on a PS layer were not significantly varied with the PS MW in the range 8 to 500,000, which could be attributed to similar surface energies of PS films [5]. Although the surface energies of the fabricated PS films were also comparable in our results, the surface roughness was quite different. This result suggests that the smoother surface of gate dielectric layer forms the larger pentacene grains in size. Such an interrelation between the surface roughess of gate dielectric layer and the grain size of the organic semiconductor film is well coincident with many previous works [9, 10]. Interestingly, as shown in inset of Fig. 3, the molecules in a channel regime which induced at the insulator-semiconductor interface within a range of a few nm thick significantly affected by the PS surface according to the molecular weight. With increasing the molecular weight of PS, less void sites were observed at the initial pentacene growth. It results from the smooth surface of PS-H layer. Note that void sites act as a kind of barrier for the charge transport at the channel region during the device operation [11]. Based on the fact that charge transport mainly occurs at the channel region [12], initial pentacene molecular growth together with 60-nm-thick pentacene AFM images would be a good evidence for analyzing the current-voltage characteristics.

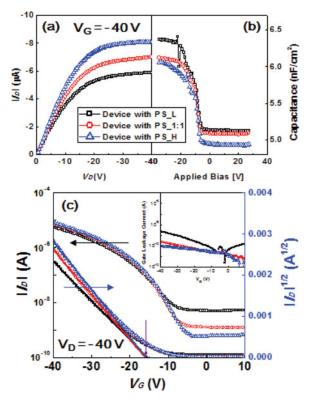

The output characteristic curve, drain current  $(I_D)$  versus drain voltage  $(V_D)$ , of the fabricated pentacene TFTs with different gate dielectric layers is shown in Fig. 4(a). Note that the output curve was observed at the gate voltage  $(V_G)$  of -40 V. The highest value of the saturation current is observed for the PS-H gate dielectric layer used case. The large drain current results from the large grain size of pentacene molecules induced from less rough surface of PS insulator. Note that higher dielectric capacitance of a gate insulator leads larger drain current at the fixed gate voltage, in other words, higher capacitance can reduce the operating gate voltage for obtaining a required level of drain current. Interestingly, in our results, the highest saturation current for the OTFT with the PS-H type was achieved with even lowest its dielectric capacitance value shown in Fig. 4(b), which is measured from the capacitance-voltage (C-V) characteristics of metal-insulatorsemiconductor (MIS) capacitor. Important device properties are extracted from the transfer characteristic plots of  $\log_{10}|I_D|-V_G$  and  $|I_D|^{1/2}-V_G$  at a negative  $V_D$  of -40 V, shown in Fig. 4(c). Among three different types of organic transistors, the highest saturation-region mobility of 0.28 cm<sup>2</sup>/Vs for our results was obtained for the device with the PS-H gate dielectric layer. Since the largest pentacene grains grew on the PS-H film, an increase in the mobility can be attributed to less grain boundaries in the pentacene film grown on the

| 11 13 with different 15 dielectric layers |                          |                                |                                  |

|-------------------------------------------|--------------------------|--------------------------------|----------------------------------|

| Gate<br>Dielectric                        | Threshold<br>Voltage (V) | Mobility (cm <sup>2</sup> /Vs) | Subthreshold Slope<br>(V/decade) |

| PS-L                                      | -16                      | 0.18                           | 7.92                             |

| PS-B                                      | -16                      | 0.25                           | 4.80                             |

| PS-H                                      | -16                      | 0.28                           | 4.22                             |

**Table 1.** The electrical properties of the fabricated three types of pentacene TFTs with different PS dielectric layers

PS-H gate dielectric layer [13]. Detailed device parameters are summarized in Table 1. Most importantly, the highest leakage currents in the off-state region are observed for the OTFT with the PS-L gate dielectric layer. The inset of Fig. 4(c) also shows conspicuous leakage currents through the gate electrode for the PS-L case. Assuming that the pentacene active layer is totally depleted in the off-stage region under positive  $V_G$ , it is possible that more defects generated by ambient molecules might give rise to deep-level traps at the interface between the pentacene and gate dielectric layers so that such traps presumably act as a gate-leakage source. Indeed, ambient molecules such as  $H_2O$  and  $O_2$  can permeate

**Figure 4.** (a) Output characteristics of the fabricated OTFTs and (b) plots of *C-V* characteristics measured with the MIS capacitors according to gate dielectric layers. (c) Transfer characteristics of the fabricated pentacene TFTs. The inset shows the leakage currents—gate voltage curves of the transistors.

easily into the pentacene film having relatively small grains through a large amount of grain boundaries. Although systematic analysis on leakage behavior could not be demonstrated in the present study, it is clearly true that traps are significantly related with gate-leakage exhibitions [14,15]. Consequently, we believe that proper optimization for the molecular weight of polymeric gate-dielectric materials is a prerequisite for the performance of OTFTs.

#### Conclusion

We investigated the characteristic dependence of pentacene-based OTFTs on the molecular weight of polymeric gate dielectric material. With our firsthand experimentations, large pentacene grains in size and traps induced by interface defects are found to be decisive for the saturation drain current  $I_D$  in the on-state and leakage currents in the off-state of OTFTs, respectively. This work demonstrates that a polymeric insulator with higher molecular weight is a promising candidate as an organic-based gate dielectric material for high-performance OTFTs due to low leakage currents as well as high drain currents during device operation, which must be resulted from larger pentacene grains on its smooth surface. Accordingly, we can conclude that the electrical performance of OTFTs is closely related with the molecular weight of polymeric gate dielectric materials. Further studies on other polymeric dielectric materials with various molecular weights still remain to be carried out. This work would provide a scientific platform to build up a high performance showing organic electrical devices.

#### Acknowledgments

This research was supported by Hallym University Research Fund, 2014(HRF-2014). This work was also supported by Basic Science Research Program through the National Research Foundation of Korea (NRF) funded by the Ministry of Education, Science and Technology (NRF-2012R1A1A2043958).

#### References

- [1] Facchetti, A., Yoon, M.-H., & Marks, T. J. (2005). Adv. Mater., 17, 1705.

- [2] Suemori, K., Uemura, S., & Kamata, T. (2008). Appl. Phys. Lett., 93, 033308.

- [3] Kim, H. B., & Oh, T. (2006). Jpn. J. Appl. Phys., 45, 7871.

- [4] Park, B. J., Sung, J. H., & Choi, H. J. (2008). J. Nanosci. Nanotechnol., 8, 2676.

- [5] Choi, H. H., Lee, W. H., & Cho, K. (2012). Adv. Funct. Mater., 22, 4833.

- [6] Liu, Y. Q., Sun, X. N., Di, C. A., Wen, Y. G., Guo, Y. L., Zhang, L., Zhao, Y., & Yu, G. (2011). Adv. Mater., 23, 1009.

- [7] Tsukagoshi, K., Miyadera, T., Wang, S. D., Minari, T., & Aoyagi, Y. (2008). Appl. Phys. Lett., 93, 033304.

- [8] Benor, A., & Knipp, D. (2008). Org. Electron., 9, 209.

- [9] Steudel, S., Vusser, S. D., & Heremans, P. (2004). Appl. Phys. Lett., 85, 4400.

- [10] Yang, S. Y., Shin, K., & Park, C. E. (2005). Adv. Func.. Mater., 15, 1806.

- [11] Bae, J.-H., Kim, W.-H., Kim, H., Lee, C., & Lee, S.-D., J. Appl. Phys. 102, 063508 (2007).

- [12] Dinelli, F., Murgia, M., Levy, P., Cavallini, M., Biscarini, F., & de Leeuw, D. M. (2004). Phys. Rev. Lett. 92, 116802.

- [13] Di Carlo, A., Piacenza, F., & Maresch, H. (2005). Appl. Phys. Lett, 86, 264501.

- [14] Lee, J., Kim, K., & Im, S. (2003). Appl. Phys. Lett., 82, 23.

- [15] Mun, S., Choi, J., Lee, K. H., & Im, S. (2008). Appl. Phys. Lett., 93, 233301.